Co by było, gdyby Państwa dysk twardy mógł myśleć razem z Państwa danymi? Zamiast tylko przechowywać pliki, proszę sobie wyobrazić, że przetwarza on informacje i reaguje na nie dokładnie tam, gdzie są przechowywane. Na tej zasadzie opierają się obliczenia w pamięci - rosnąca zmiana w architekturze, która przenosi logikę bliżej pamięci w celu zwiększenia wydajności.

Naukowcy z Forschungszentrum Jülich i Uniwersytetu Duisburg-Essen zaprezentowali nowy projekt oparty na memrystorach 2T1R, który może wspierać tę zmianę, umożliwiając bardziej energooszczędną sztuczną inteligencję i sprzęt brzegowy.

Opublikowany na stronie arXivw projekcie zintegrowano dwa tranzystory i jeden memrystor na komórkę, z regulacją prądu mającą na celu tłumienie prądów ścieżki podkradania, co jest znanym wyzwaniem w matrycach memrystorowych. W przeciwieństwie do konwencjonalnej pamięci, proponowany projekt uziemia oba terminale memrystora w stanie bezczynności - strategia, która może pomóc poprawić stabilność sygnału i zmniejszyć wyciek.

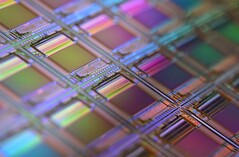

Architektura została zaprojektowana do obsługi analogowego mnożenia wektorowo-matrycowego (VMM), podstawowej funkcji w uczeniu maszynowym, poprzez kontrolowanie przewodności memrystora za pomocą zintegrowanych przetworników cyfrowo-analogowych, sygnałów PWM i regulowanych ścieżek prądowych. Układ testowy 2×2 został pomyślnie zaimplementowany przy użyciu standardowej technologii CMOS 28 nm.

Dzięki rozwiązaniu kwestii wirtualnego uziemienia i efektów rezystancji przewodów, architektura ma na celu poprawę przewidywalności wydajności i zmniejszenie zużycia energii. Dzięki kompatybilności ze sterowaniem RISC-V i cyfrowym interfejsem, projekt 2T1R może położyć podwaliny pod skalowalne chipy neuromorficzne, umożliwiając szybszą, bardziej kompaktową akcelerację sztucznej inteligencji bezpośrednio w pamięci.

Podczas gdy Państwa dysk twardy może jeszcze nie myśleć, architektura stojąca za tą wizją już nabiera kształtu w krzemie - wskazując na przyszłość szybszej, zintegrowanej z pamięcią sztucznej inteligencji.

Aby uzyskać szczegółowe informacje techniczne i wyniki, proszę zapoznać się z pełnym preprintem arXiv (PDF).